Overall Risk, currently Lower 25D needs fewer new capabilities Need for standards Lower VerticalstackingMorecoordination 25D and 3D solutions can be combined in one IC package ! 5221 Major Benefits of 25D Ic Packaging Over the Traditional 2D Packaging Practices 523 3D Ic Packaging Technology 524 2D Vs 25D Vs 3D Ic Packaging Technology 53 System in Package (SIP2D vs 25D vs 3D Carving Part 36 Aspire and VCarve For Absolute BeginnersMore down here ↓↓↓ Click SHOW MORE!This is the 36th in a series of videos geare

Www Nist Gov Document Bottomspdf

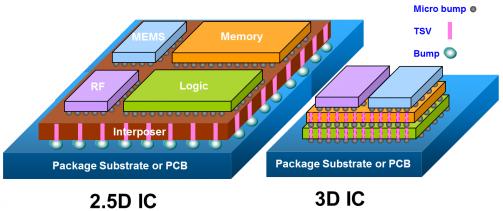

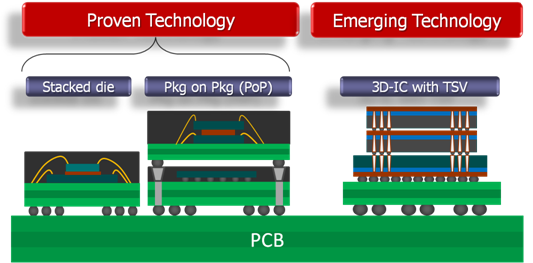

2.5 d vs 3d packaging

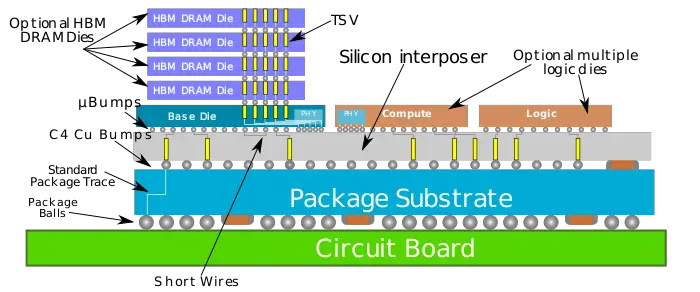

2.5 d vs 3d packaging-And 3D systems integration This video, 3D Chip Technology for Dummies, from Applied Materials, breaks it down in very easy25D/3D TSV Meet high performance, low energy demands Through Silicon Via (TSV) interconnects have emerged to serve a wide range of 25D TSV and 3D TSV packaging applications and architectures that demand very high performance and functionality at the lowest energy/performance metric

System In Package Ase Group

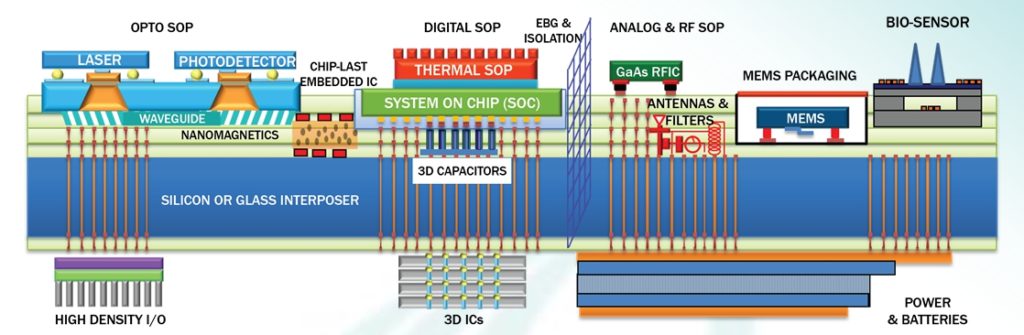

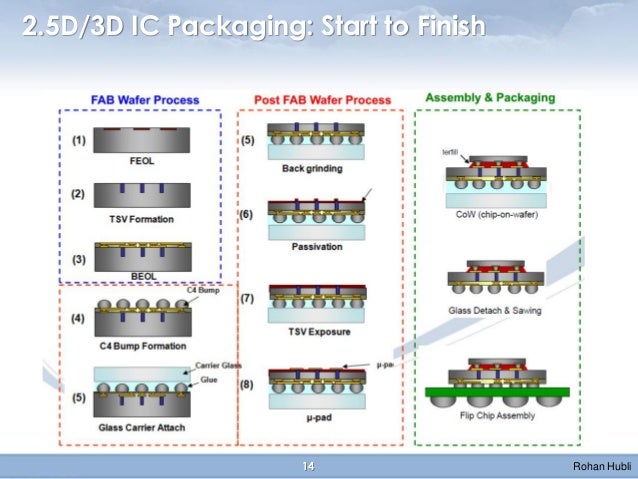

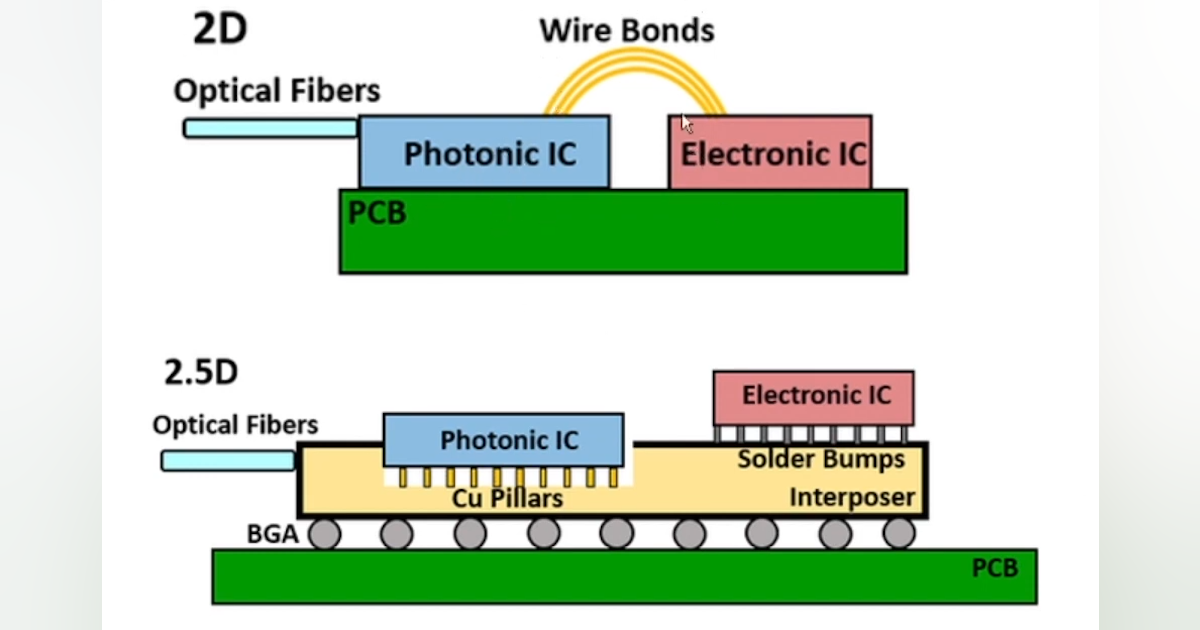

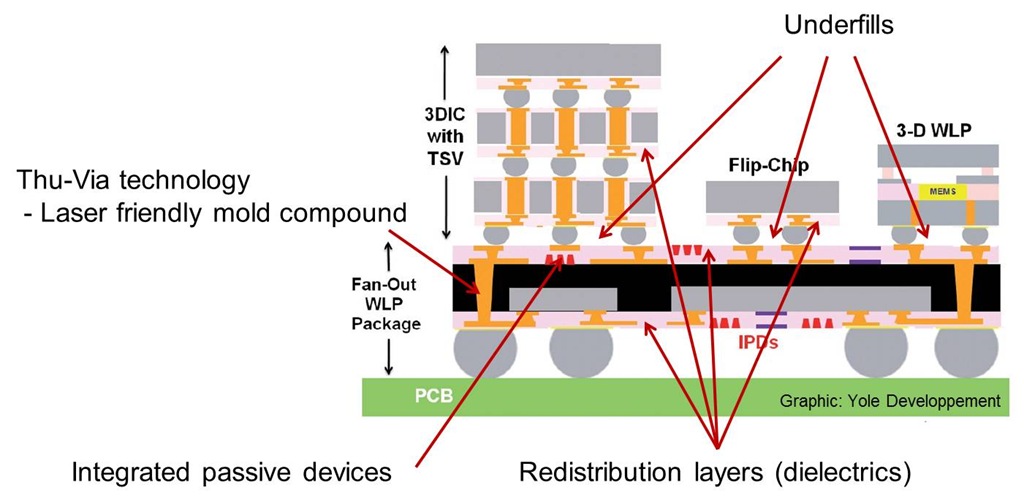

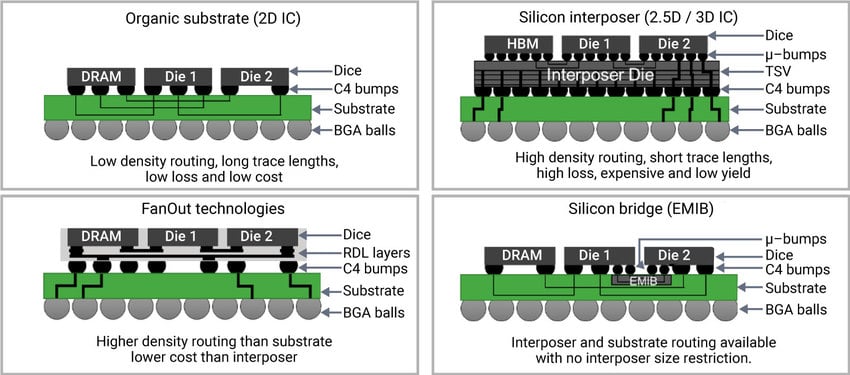

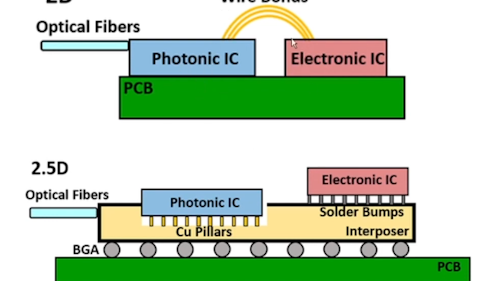

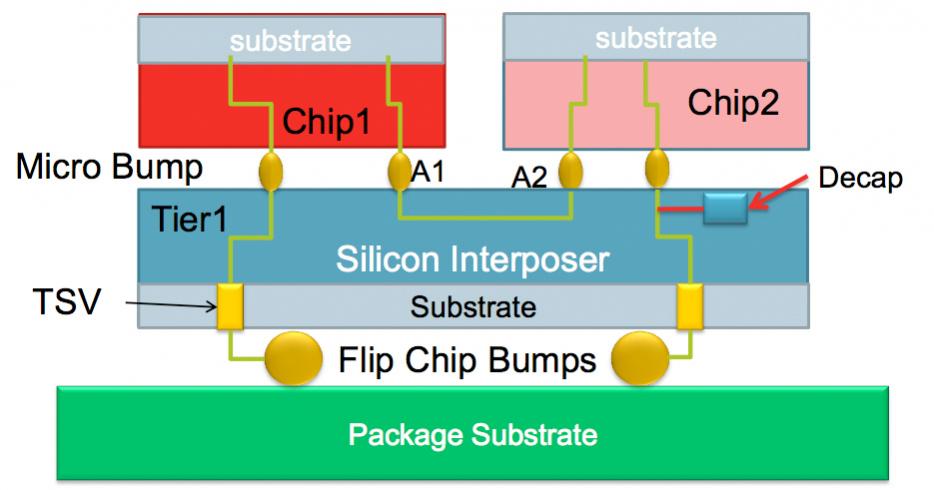

The material presented will also reference 3D packaging standards and recognize innovative technologies from a number of industry sources, roadmaps and market forecasts Key words 25D, 3D Semiconductor Package Technology, Through Silicon Via, TSV, Through Glass Via, TGV Together with 25D/3D packaging this extends Moore's Law at systemlevel" Without a doubt, times have changed, highend performance packaging is enabling systemlevel 25D/3D integration trendPackaging Technologies GF Si nodes are qualified in a wide range of package technologies including 2D wirebond designs, flip chip, WLCSP and FOWLP configurations, as well as 25D, 3D and SiPhotonics The 25D package technologies leverage GF TSV Si interposer technology using 65nm and 32nm process node design rules,

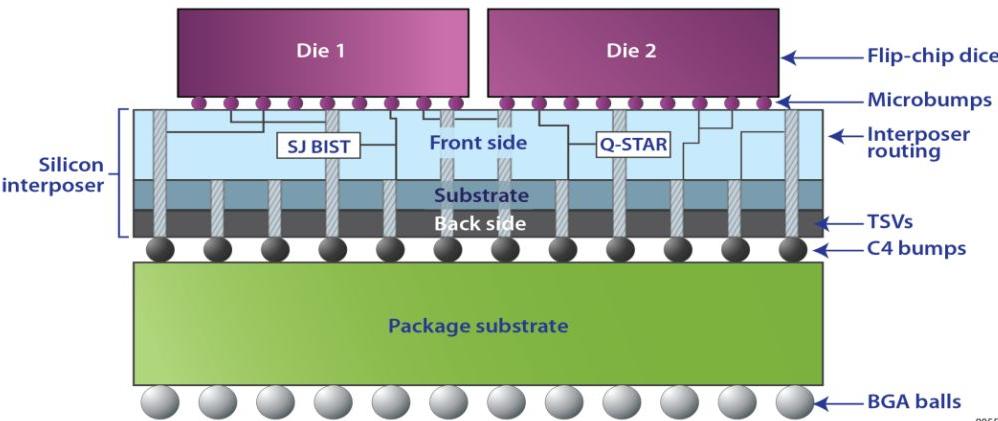

25D & 3D Packaging Indium Corporation is a world leader in the design, formulation, manufacture and supply of semiconductorgrade fluxes and associated materials, enabling 25 and 3D assembly processes, as well as more standard flipchip assembly There are many different substrates that are used in the electronics industry, and some are more 25D and 3D Wafer Level Packaging (Si/Glass interposer, 3DIC) # 25/3D wafer level packaging is one of the important key technologies in advanced microelectronic packaging and system integration worldwide This concept has specific advantages in terms of heterogeneous integration of multiple devices such as sensors, processors, memory ICs andXRM vs microCT technology Increasing the success rates of PFA The following case study demonstrates the benefits that 3D XRM offers to chipmakers In this instance, a 25D interposer test chip with microbumps was used for packaging development and process optimization In the center of Figure 5 is the package computeraided design (CAD) layout,

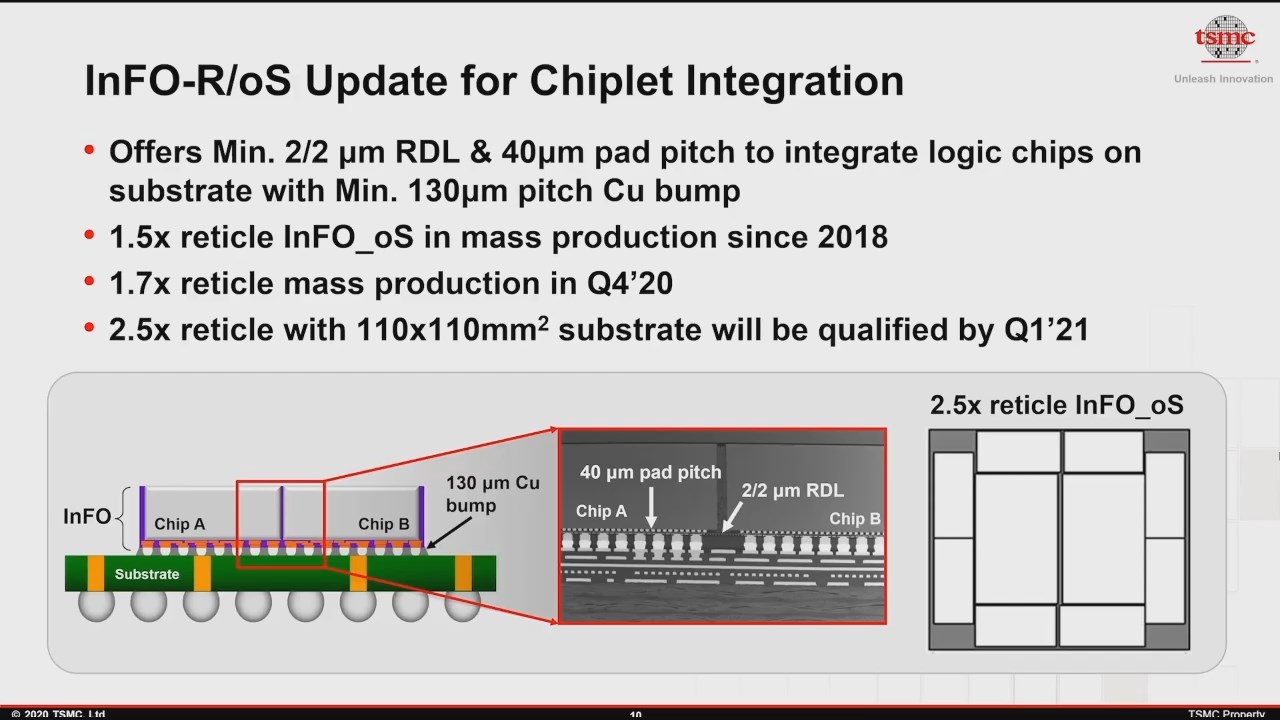

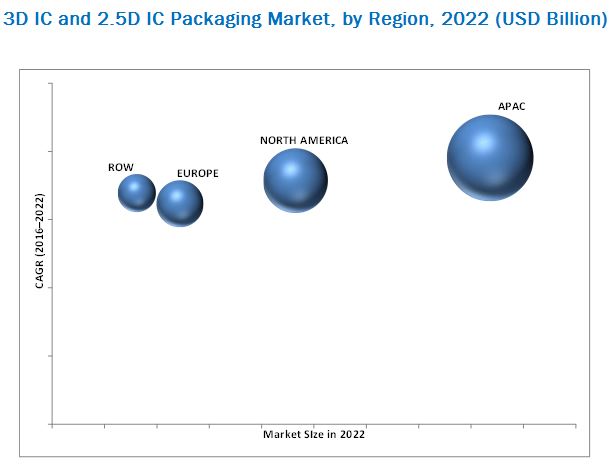

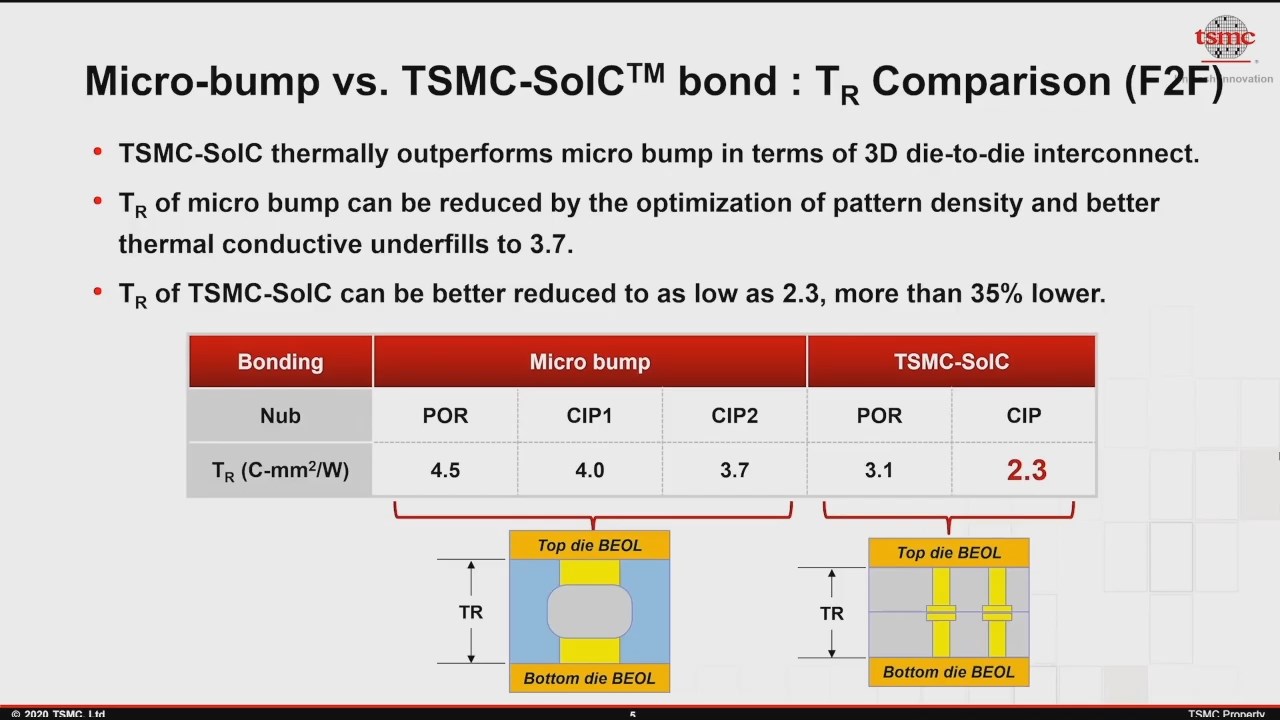

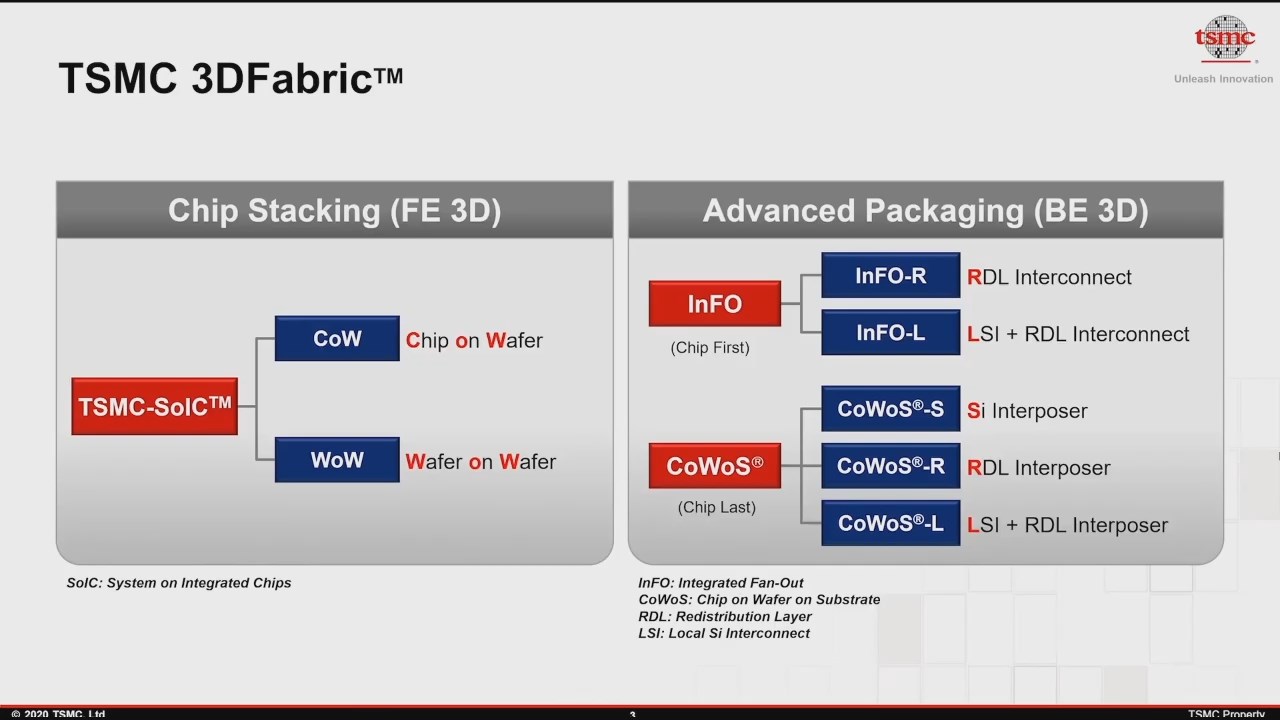

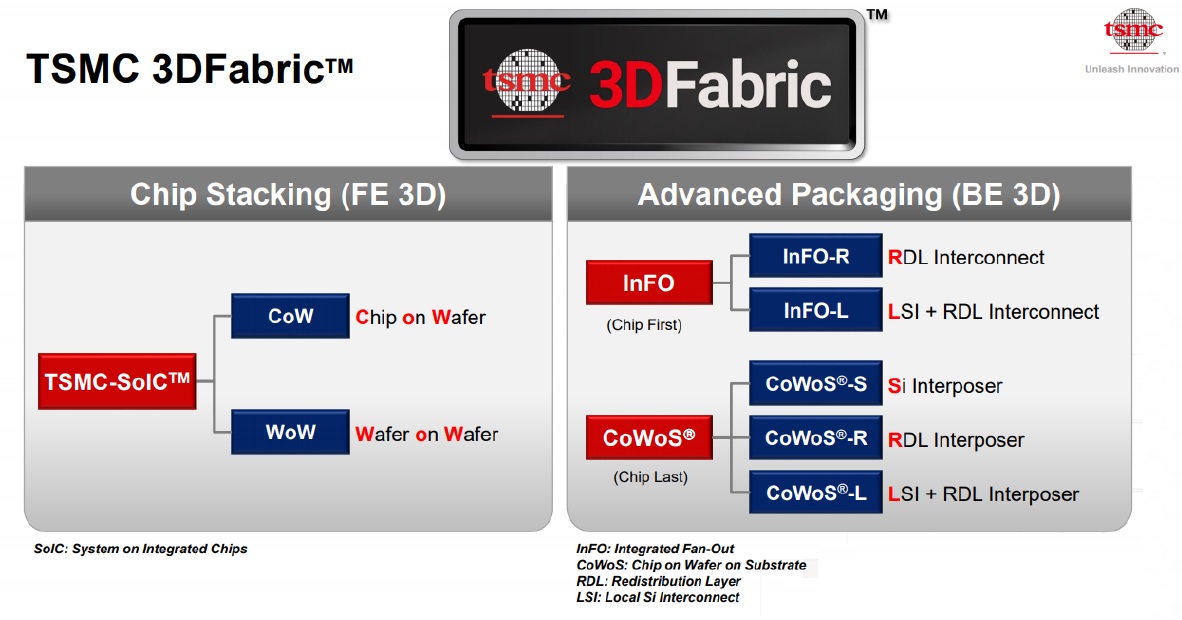

25D/3D packaging Recently, TSMC held their 26th annual Technology Symposium, which was conducted virtually for the first time This article is the second of three that attempts to summarize the highlights of the presentations This article focuses on the TSMC advanced packaging technology roadmap, as described by Doug Yu, VP, R&D 33 Global 3D IC and 25D IC Packaging Revenue by Region 16 VS 21 VS 27 34 Global Top 3D IC and 25D IC Packaging Regions by Sales 341 Global Top 3D IC and 25D IC Packaging Regions by25D and 3D interposerbased integration;

Insights From Leading Edge Insights From Leading Edge Page 4

Q Tbn And9gcs6rwxysyiknusgwh6hlnqxczejucgowt5six9512lxjbfp4n Usqp Cau

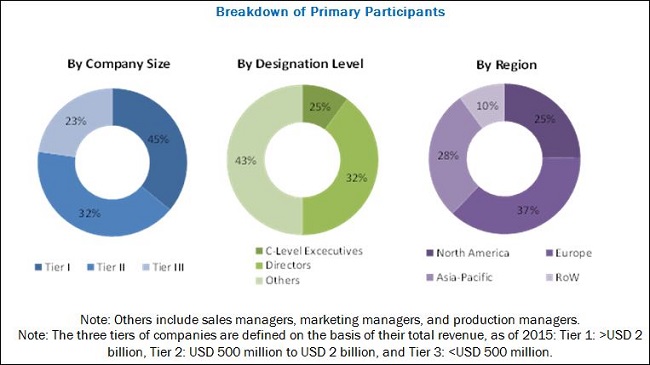

3D IC and 25D IC Packaging Market Report study provides in detail information to understand the imperative market parts that aligns with the business decision related to raw materials, demand, and production capacity The analysis provides demands for the future, besides the opportunities that are available for individualTong expects commercialization of 25D chip technology to take place in two years Tong notes that 25D IC should notbe regarded as a transitional integration technology" Si Interposer "25D will enable packaging of chips in the 3222 nm nodes where the fragile mechanical stability of the lowK dielectrics used in these products will require 25D vs Fanout Chip on Substrate WeiHong Lai 12/8/ Technology The demand for high bandwidth and highperformance applications such as networking, AI computing and GPU IC chips are driving innovative developments in advanced IC packaging Heterogeneous integration enables the integration of multiple chips using fine line/space

2 5d Semiconductor Engineering

Semiconductor Packaging 3d Ic Emerging As Innovation Enabler Semiwiki

The Market Needs a New Kind of 3D Field Solver As shown in the figure below, the 25D and 3D parasitic extraction tools market currently consists of Finite element method (FEM)/boundary element method (BEM) tools (3D), which use numerical solvers to 25/3D Level Heterogeneous Integration • Heterogeneous Integration • In the context of describing 25D/3D packaging level of technology • Integrating dissimilar chips using a packaging technology with I/O density higher than organic substrate (Feature size smaller than organic substrate, or 3D die) • Technology drivers • High bandwidthThe material presented will also reference 3D packaging standards and recognize innovative technologies from a number of industry sources, roadmaps and market forecasts Key words 25D, 3D Semiconductor Package Technology, Through Silicon Via, TSV, Through Glass Via, TGV

Fan Out Wafer Level Packaging The Samtec Blog

High End Performance Packaging

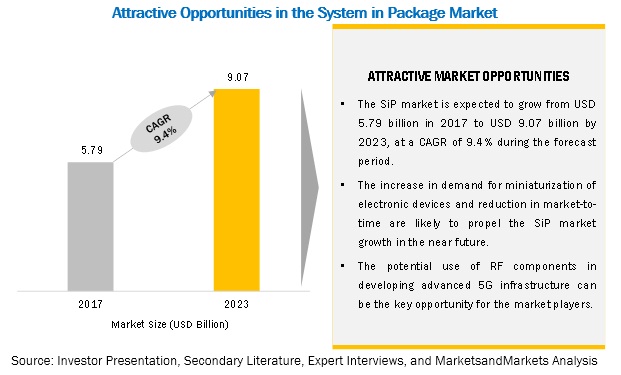

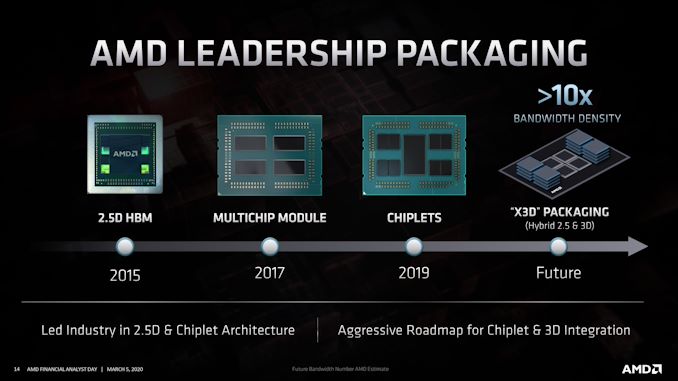

The 3D IC and 25D IC Packaging market in the US is estimated at US$26 Billion in the year China, the world`s second largest economy, is forecast to reach a projected market size of US$1241 Billion by the year 27 trailing a CAGR of 346% over the analysis period to 27Together with 25D/3D packaging this extends Moore's Law at systemlevel Times have changed The industry is seeking alternatives to design and manufacture the latest Systems on Chips (SoCs) using System in Package (SiP) and chipletbased approaches by leveraging HighEnd Packaging to mix both the latest and mature nodes 25D/3D packaging AMD Discusses 'X3D' Die Stacking and Packaging for Future Products Hybrid 25D and 3D One of AMD's key messages at its Financial Analyst Day is that the company wants to remain on the

Intel Leans Hard On Advanced Chip Packaging Technologies In Battle For Computing Supremacy Venturebeat

More 2 5d 3d Fan Out Packages Ahead

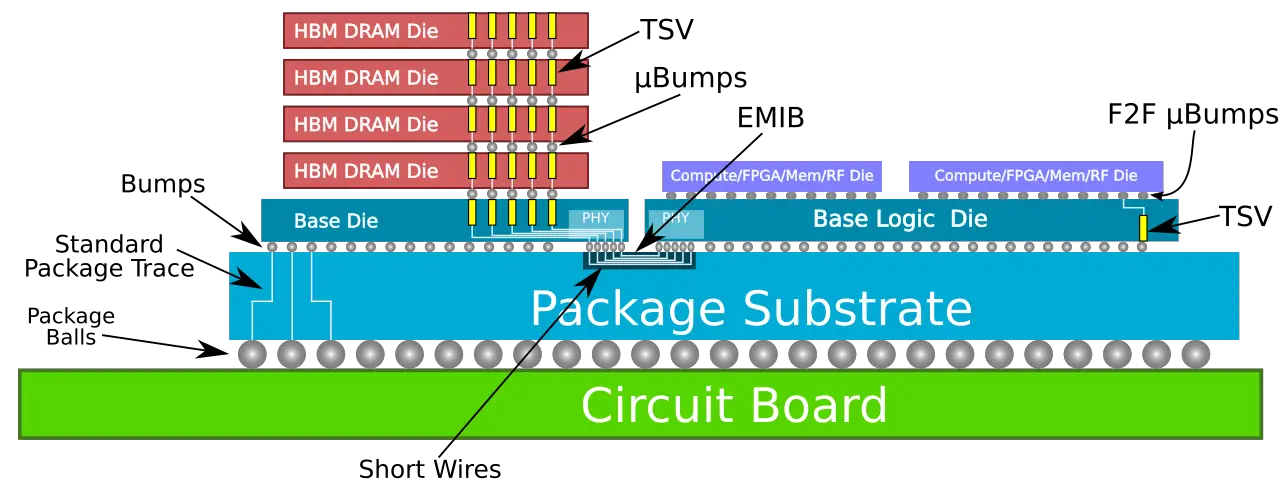

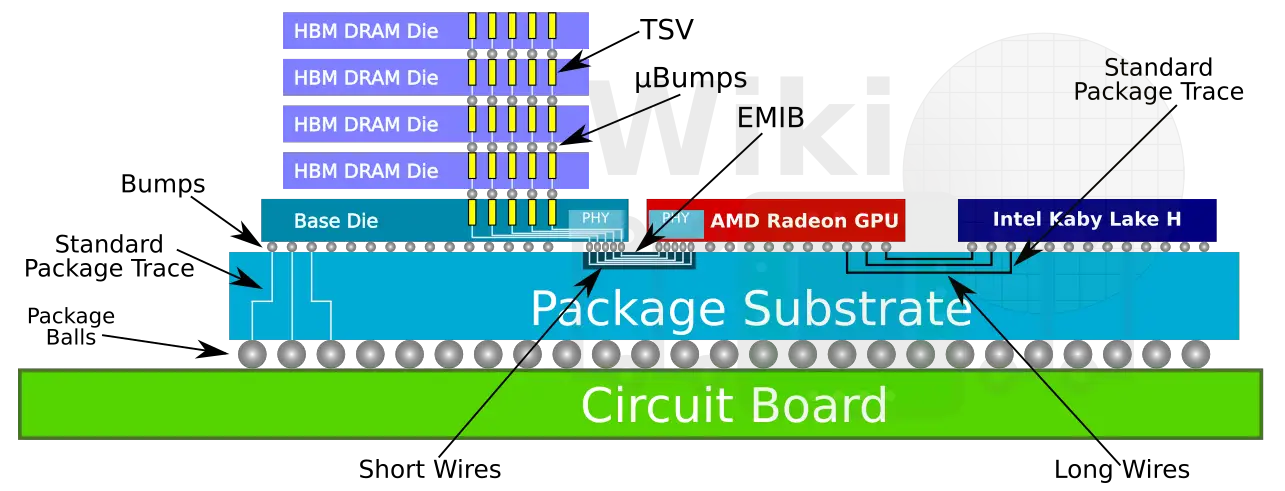

David Schor 25D packaging, 3D packaging, CoEMIB, EMIB, Foveros, Intel A look at ODI, a new family of packaging interconnect technologies that bridges the gap between Intel's EMIB (25D) and Foveros (3D) by providing the flexibility of an EMIB in 3D with additional benefits of thermal & power Read more• This report is an update of the previous 17 release "3D TSV and 25D business update Market and Technology trends 17" • The scope of this report is to present the actual trends and their impact on the packaging need and especially the 25D/3D stacking technologies What you've done is transferred the problem to another guy, the packaging guy" How important is it to have 3D die stacking vs the 25D approach?

Advanced Packaging Five Trends To Watch In 17 Electronic Products

3d Ic And 2 5d Ic Packaging Market By Application Logic Imaging 22 Marketsandmarkets

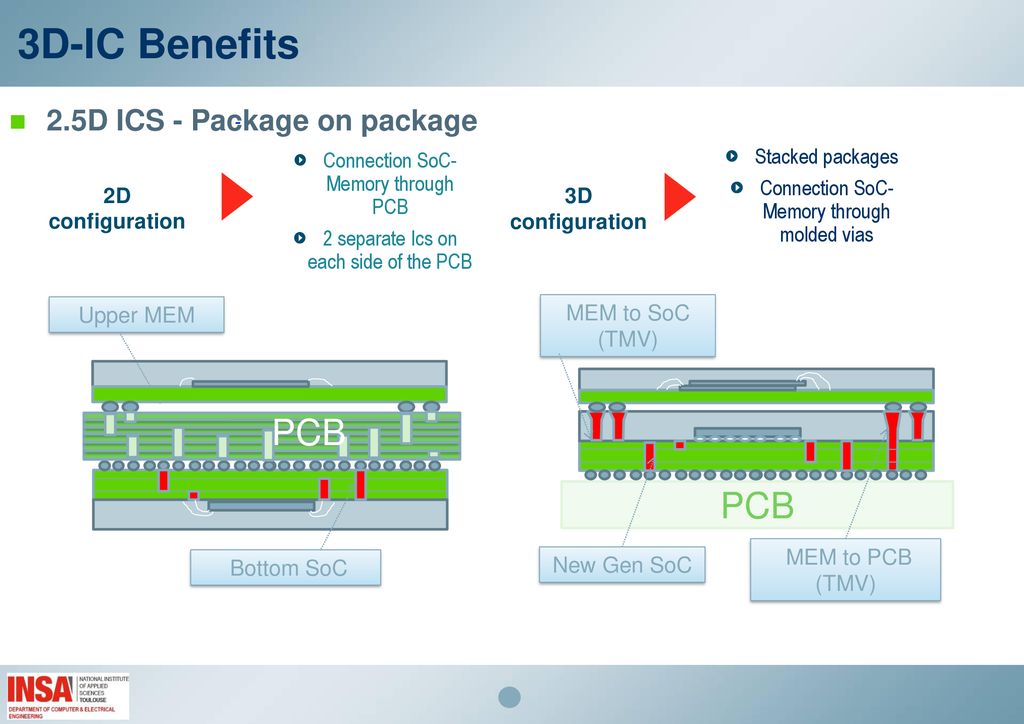

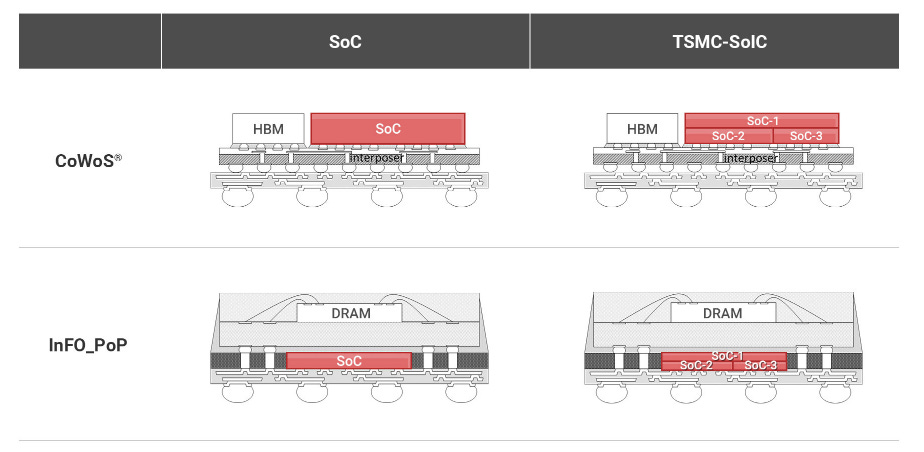

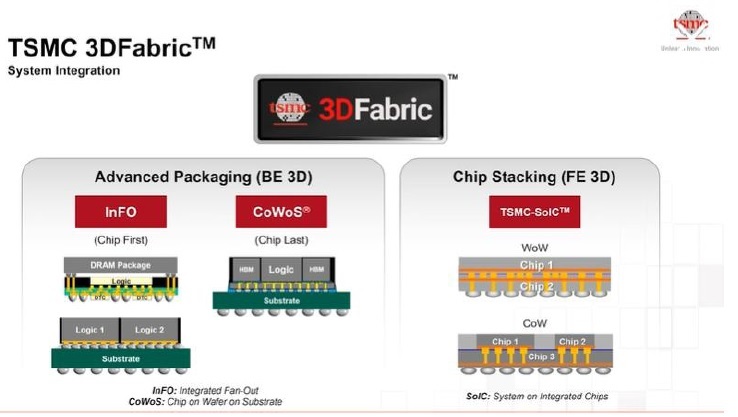

In order to unify all the different names it gives to its variants of its 25D and 3D packaging, TSMC has introduced its new overriding brand 3DFabric 3DFabric makes sense as a brand to tie the Above Blending 25D and 3D packaging technologies yields CoEMIB, which enables largerthanreticle sized base dies plus Foveros die2D, 21D, 25D, and 3D Package Studies in NEPP Eric J Suh Joseph Riendeau Jet Propulsion Laboratory, California Institute of Technology NASA Electronic Parts and Packaging Program (NEPP) 19 Annual NEPP Electronic Technology Workshop (ETW) June 18th, 19 1

3d Ic Emc Ppt Download

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

The overall stacking technologies market will exceed US$55 billion in 23 with a CAGR of 27%, announces Yole it its latest advanced packaging report, 25D / 3D TSV & Wafer Level Stacking Technology & Market Updates report As for today, the consumer market is the biggest contributor, with over 65% market shareBe sure to subscribe to our channel by clicking this link http//bitl 145 Middle East and Africa 3D IC and 25D IC Packaging Sales Breakdown by Type (1621) 2 Global 3D IC and 25D IC Packaging Market Competition by Company 21 Global Top Players by 3D IC and

Eps Ieee Org Images Files Hir 19 Hir1 Ch22 2d 3d Pdf

Intel Looks To Advanced 3d Packaging For More Than Moore To Supplement 10 And 7 Nanometer Nodes Page 2 Wikichip Fuse

3D and 25D packaging has been heralded as a set of the best package architectures to satisfy shrinking time to market windows while offering an effective way to combine the ever increasing set of circuits needed for today's popular products There is significant confusion as to the design guidelines and the economics involved to create a 3D Foundries involved in 3D/25D IC packaging P1 • Key players • Technological capability • Installed capacity • 3D/25D IC packaging roadmap • Recent activities • Key customers • Opportunities & Challenges • Outlook & Summary XIV Conclusion P0 XV Appendix P5 • TSV technology • TSV integration schemes • Via first vs The Japanese brand, wellknown for its famous watches, is exploring a new print technology, called 25D printing As its name suggests, this print technology lies somewhere between 2D and 3D printing The 25D printing technology adds a tactile dimension to 2D printing, allowing users to touch and feel the surface and texture of the printed object

Amd Discusses X3d Die Stacking And Packaging For Future Products Hybrid 2 5d And 3d

Q Tbn And9gcrvzzge1ug K9 6zczthx8vvyizrtc2hrjsqcgcvxrbn6j A I Usqp Cau

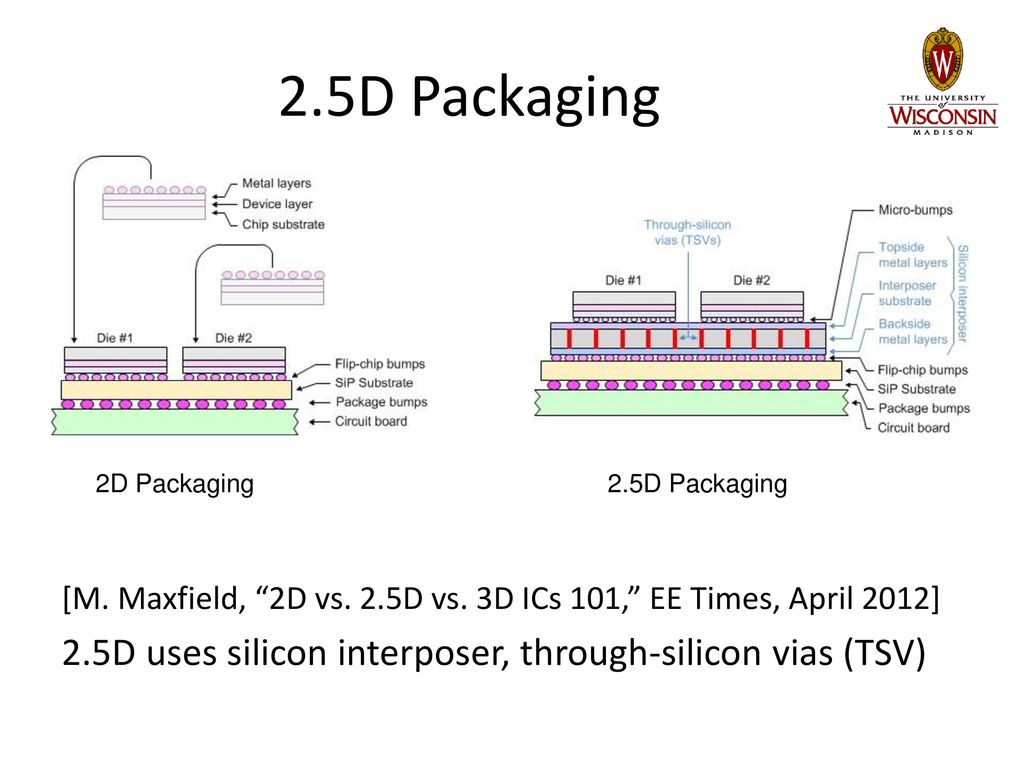

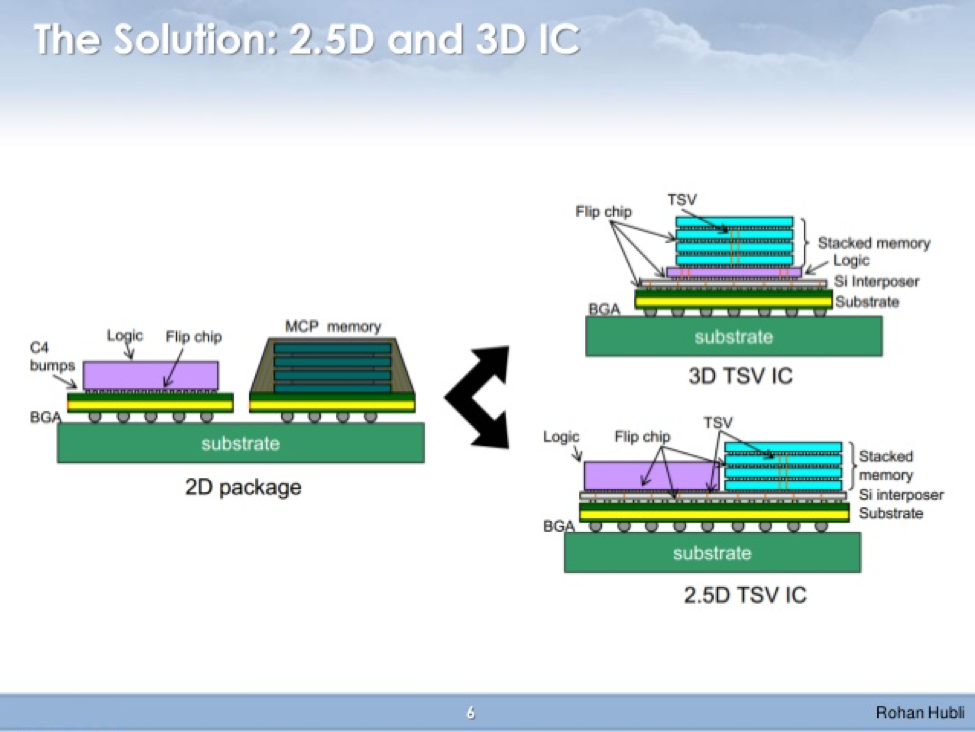

3D stacked ICs (3DSICs), monolithic 3D ICs;Madden "The idea that you need true 3D stacking is a problem in the industry it's the great being the enemy of the good Yeah, it's great to say you're going to stack 3 dies on top of each otherA 25D integrated circuit (25D IC) combines multiple integrated circuit dies in a single package without stacking them into a threedimensional integrated circuit (3DIC) with throughsilicon vias (TSVs) The term "25D" originated when 3DICs with

Lost In The Advanced Ic Packaging Labyrinth Know These 10 Basic Terms Edn

About 2 5d Technology Nhanced Semiconductors Inc

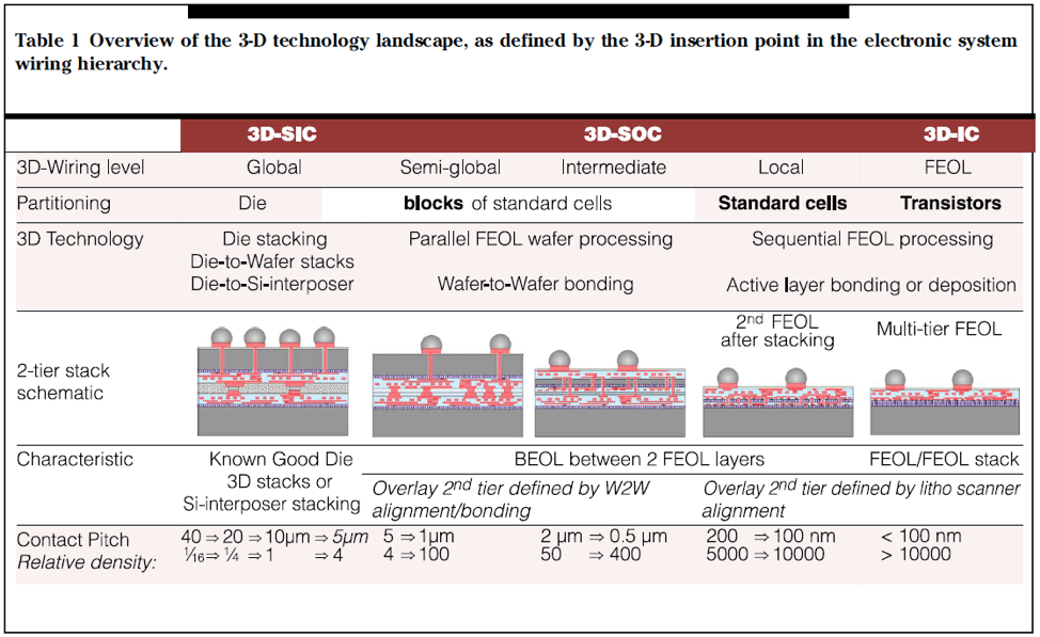

3D System on Chip * √ √ Silicon photonics √ √ √ √ 3D Stacked IC find their place in performance demanding applications * 3D System on Chip consists in logiconlogic and memoryonlogic stacked 3D IC Glass vs Silicon Interposers for 25D and 3D IC Applications There has been enough interest stirred up in R&D around glass as a lowcost alternative interposer substrate material compared with silicon, that there was an entire session dedicated to developments in that area at the 12 IMAPS International Device Packaging conference, heldQuick video explaining what a 25D video game is Thank you for watching Game Domain!

A Schematics Of The Three Integration Approaches 2d 3d And 2 5d Download Scientific Diagram

Advanced Packaging Five Trends To Watch In 17 Electronic Products

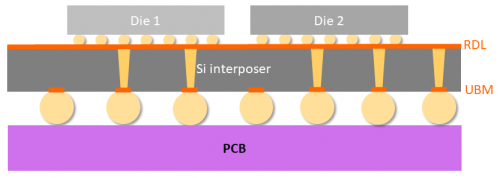

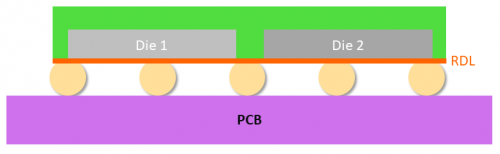

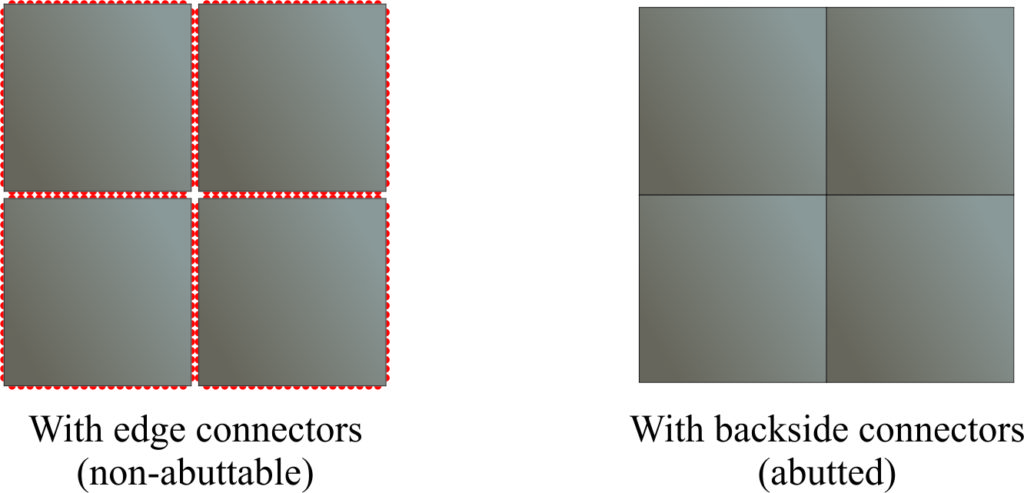

25D is a packaging methodology for including multiple die inside the same package The approach typically has been used for applications where performance and low power are critical Communication between chips is accomplished using either a silicon or organic interposer, typically a chip or layer with throughsilicon vias for communication 3D Ic And 25D Ic Packaging Market Research Scope Covers the Following Chapters Chapter 1 is the basis of the entire report In this chapter, we define the market concept and market scope of 3D 2D vs 25D vs 3D ICs 101 By Max Maxfield 6 I see a lot of articles bouncing around the Internet these days about 25D and 3D ICs One really good one that came out recently was 25D ICs are more than a stepping stone to 3D ICs by Mike Santarini of Xilinx On the other hand, there are a lot of other articles that have "3D ICs

Advanced Packaging Confusion Athisnews

Global 3d Ic And 2 5d Ic Packaging Market 17 Taiwan

A threedimensional integrated circuit (3D IC) is a package with multiple layers of silicon wafers stalked together, along with electronic components using throughsilicon vias (TSVs),while a 25dimensional integrated circuit (25D IC) is a package with an active electronic components (for example, a die or a chip) stacked on an interposer through conductive bumps or TSVs25D – also called interposer technology – integrates several electronic devices inside a single package by assembling them sidebyside on a shared base The base, an interposer, provides connectivity The devices are generally manufactured separately and delivered to the assembly house as bare dies The interposer is essentially a large25D animation is a 2D animation drawn into a 3D space as it involves the motion of 2Danimated object in a 3D space The trick lies behind the perspective and shadows of 2Danimated objects drawn in 2Dspace that appears to be 3D Animators use the impression of drawing 2D objects in motion that appears to be moving in a 3D space accomplished by using brilliant art skills in

Flip Chip Technology Market Report 18 Segmentation By Wafer

2 5d Fo Wlp Issues Come Into Focus

ASE is one of the pioneers in 25D/3D packaging technology and has successfully introduced the mass production of the world's first 25D IC package equipped with High Bandwidth Memory (HBM) 25D refers to die stacking package using interposers to achieve the best performance of In general, 3D integration is a broad term that includes such technologies as 3D waferlevel packaging; For example, in a 25D package, you would place three separate memory stacks on an interposer The first one is an SRAM cube, which is situated between two HBM stacks on the interposer Meanwhile, Intel recently launched a new 3D packaging technology called "Foveros"

2 5d 3d Ic Market Challenges Opportunities

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

Technology Challenges Ece Cs 752 Fall Ppt Download

1

Fan Out Chip On Substrate Ase Group

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

2 5d 3d Packaging Pradeep S Techpoints

Figure 1 From 3d And 2 5d Packaging Assembly With Highly Silica Filled One Step Chip Attach Materials For Both Thermal Compression Bonding And Mass Reflow Processes Semantic Scholar

Semicap Primer Packaging History And Primer By Mule Mule S Musings

Semiconductor Packaging Inspection Teraview

Intel Looks To Advanced 3d Packaging For More Than Moore To Supplement 10 And 7 Nanometer Nodes Wikichip Fuse

Three Dimensional Integrated Circuit Wikipedia

Heterogeneous Integration Hi Ase Group

17 European 3d Summit Making Advanced Packaging Great Again

Http Www Cetimes Com Sip 18 Download 1 Sp 2 Pdf

3d Ic And 2 5d Ic Packaging Market By Application Logic Imaging 22 Marketsandmarkets

Tsv Bist Die Level Integrity Monitors Ridgetop Group

Integrated Circuit Packaging And Gct The Samtec Blog

Www Nist Gov Document Bottomspdf

System In Package Ase Group

Insights From Leading Edge Just Another Solid State Technology Sites Site Page 21

Plasma Etch And Deposition Solutions For 2 5d 3d Packaging Spts

1

Chip Packaging Part 4 2 5d And 3d Packaging Electronic Design

/article-new/2015/11/tsmc_chip_packaging-800x400.jpg?lossy)

Patent Applications Reveal Apple S Research Into 3d Chip Packaging Macrumors

Chip On Wafer On Substrate Cowos Tsmc Wikichip

Different 3d Technologies Arranged According To Manufacturing Costs And Download Scientific Diagram

System In Package Market By Packaging Technology Package Packaging Method Device Application Covid 19 Impact Analysis Marketsandmarkets

Amd Discusses X3d Die Stacking And Packaging For Future Products Hybrid 2 5d And 3d

Design Electrical Mechanical Thermal Prc Gatech Edu Georgia Institute Of Technology Atlanta Ga

Interposer Wikipedia

Conventional Process Flow For 2 5d 3d Ic Integration Chip On Download Scientific Diagram

Http Ewh Ieee Org Soc Cpmt Presentations Cpmt1105a Pdf

Heterogeneous Integration Hi Ase Group

Polymer Challenges In Electronic Packaging Overview Polymer Innovation Blog

2 5d 3d Ase Group

2 5d Ics Or Interposer Technology Youtube

Www Ibm Com Downloads Cas M0nl8n85

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

Www Semiconductors Org Wp Content Uploads 18 06 2 15 Itrs 2 0 Herogeneous Integration Pdf

The Race To Next Gen 2 5d 3d Packages

Typical Structure Of 2 5d Ic Package Utilizing Interposer Not To Scale Download Scientific Diagram

Packaging Wars Begin

Sorting Out Packaging Options

Http Www Circuitinsight Com Pdf 2 5d 3d Semiconductor Package Technology Ipc Pdf

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

Nepp Nasa Gov Workshops Etw18 Talks 19june18 1330a sheldon nepp etw djs final Pdf

Figure 1 From 2 5d 3d Tsv Processes Development And Assembly Packaging Technology Semantic Scholar

Amkor S Advanced Packaging A Closer Look I Micronews

Semicap Primer Packaging History And Primer By Mule Mule S Musings

Advanced Semiconductor Packaging Starting To Change Memory Market Landscape Seeking Alpha

2 5d Packaging Wikichip Fuse

Sorting Out Packaging Options

Http Www Oic Co Kr Files 2 5d 3d Tsv And Wafer Level Stacking Technology And Market Sample Pdf

Plasma Etch And Deposition Solutions For 2 5d 3d Packaging Spts

Production Test Of System In Package With Die To Die Phy Ip

Iftle 468 Samsung Advanced Packaging At The Virtual Iwlpc 3d Incites

3d Ic Design Ee Times

What Is 3d Integration 3d Incites

3d Ic And 2 5d Ic Packaging Market In Depth Analysis Taiwan

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

3dfabric The Home For Tsmc S 2 5d And 3d Stacking Roadmap

3d Thursday 28nm Design And 2 5d Packaging Saves Xilinx A Ton Of Power You Can Too Even If You Re Not Designing Fpgas Eda360 Insider

Ppt Technology Challenges Ece Cs 752 Fall 17 Powerpoint Presentation Id

Pdf Cost Comparison Of 2 5d 3d Packaging To Other Packaging Technologies Semantic Scholar

Sensors In 3d And 2 5d Nhanced Semiconductors Inc

2 5d And 3d Ics New Paradigms In Asic Product Engineering Blog Einfochips

Chip Packaging Part 4 2 5d And 3d Packaging Electronic Design

2 5d And 3d Designs Semiwiki

Highlights Of The Tsmc Technology Symposium Part 2 Semiwiki

Iftle 381 Tsmc Wow Insights From Leading Edge

Pin On Telecharger Gratuit

What Is 3d Integration 3d Incites

3d Ic And 2 5 D Ic Packaging Industries In Depth Analysis

Three Dimensions In 3dic Part I Research Articles Arm Research Arm Community

Highlights Of The Tsmc Technology Symposium 21 Packaging Semiwiki

2 5d And 3d Ics New Paradigms In Asic Product Engineering Blog Einfochips

Interconnect Research At Tsmc Page 1 Research Taiwan Semiconductor Manufacturing Company Tsmc English

0 件のコメント:

コメントを投稿